- 品牌

- 京曉設計

- 服務內容

- 技術開發

- 版本類型

- 普通版

數據可視化圖表應用:用熱力圖展示PCB溫度分布(如功率器件區域溫度達85℃);以折線圖對比不同疊層結構的阻抗曲線(如4層板與6層板的差分阻抗穩定性)。案例模板:汽車電子BMSPCB設計摘要針對新能源汽車電池管理系統(BMS)的高可靠性需求,設計8層HDIPCB,采用ELIC工藝實現高密度布線,并通過熱仿真優化散熱路徑。實驗表明,在-40℃~125℃溫循測試(1000次)后,IMC層厚度增長≤15%,滿足AEC-Q100標準。關鍵詞:汽車電子;BMS;HDI;熱仿真;可靠性正文結構:需求分析:BMS需監測電池電壓/溫度(精度±5mV/±1℃),并支持CANFD通信(速率5Mbps);明確電路功能、信號類型(數字/模擬/高速)、電源需求、尺寸限制及EMC要求。高效PCB設計怎么樣

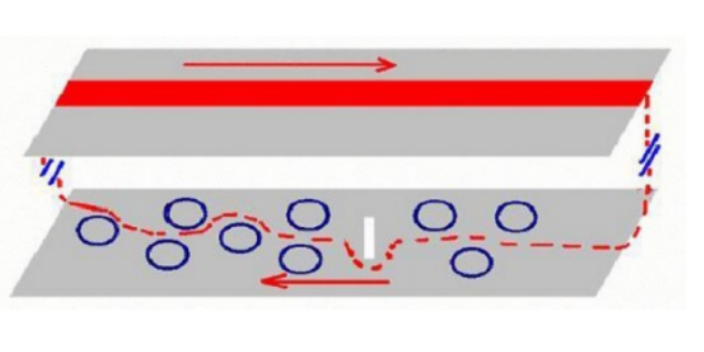

關鍵設計規則:細節決定成敗元器件布局**守則先大后小:優先布局大型元件(如CPU),再放置小元件。對稱布局:相同功能電路采用對稱設計(如雙電源模塊),提升美觀性與功能性。去耦電容布局:靠近IC電源管腳(如0.1μF電容緊貼MCU的VCC),形成**短回路。信號隔離:高電壓/大電流信號與小信號分開,模擬信號與數字信號隔離。布線優先級與技巧關鍵信號優先:模擬小信號、高速信號、時鐘信號優先布線。走線方向控制:相鄰層走線方向正交(如頂層水平、底層垂直),減少寄生耦合。阻抗匹配:差分對(如USB 3.0)嚴格等長(誤差≤5mil),等間距走線以保持阻抗一致性。蛇形走線:用于時鐘信號線補償延時,實現阻抗匹配。宜昌專業PCB設計布線隨著通信技術、計算機技術的不斷發展,電子產品的信號頻率越來越高,對 PCB 的高速設計能力提出了挑戰。

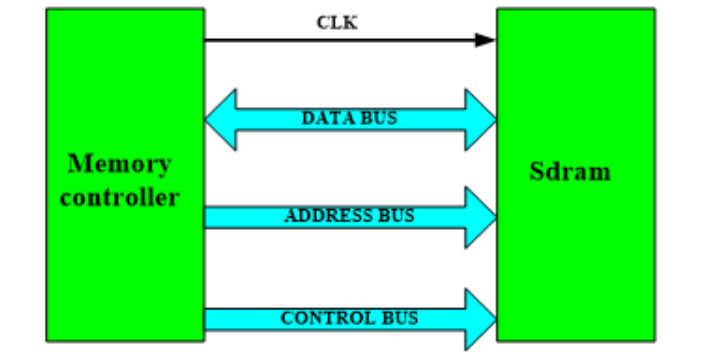

輸出制造文件Gerber文件:生成各層布局的Gerber文件,包括頂層、底層、內層、絲印層、阻焊層等。鉆孔文件:生成鉆孔數據文件,包括孔徑大小、位置等信息。裝配文件:生成元件坐標文件(如Pick & Place文件),供貼片機使用。二、PCB設計關鍵技術1. 高速信號設計差分信號傳輸:采用差分對傳輸高速信號,減小共模噪聲和電磁干擾(EMI)。例如,USB 3.0、HDMI等接口均采用差分信號傳輸。終端匹配:在信號源和負載端添加匹配電阻,減小信號反射。匹配電阻值需根據信號特性和傳輸線阻抗確定。串擾抑制:通過增加走線間距、采用屏蔽層或嵌入式電磁帶隙結構(EBG)等技術,減小串擾幅度。

高速信號設計(如DDR、USB 3.1)等長控制:通過蛇形走線(Serpentine)實現差分對等長,誤差控制在±50mil以內;端接匹配:采用串聯電阻(如22Ω)或并聯電容(如10pF)匹配傳輸線阻抗,減少反射;拓撲優化:DDR4采用Fly-by拓撲替代T型拓撲,降低信號 skew(時序偏差)至50ps以內。高密度設計(如HDI、FPC)微孔加工:激光鉆孔實現0.1mm孔徑,結合盲孔/埋孔技術(如6層HDI板采用1+4+1疊層結構),提升布線密度;任意層互連(ELIC):通過電鍍填孔實現層間電氣連接,支持6層以上高密度布線;柔性PCB設計:采用PI基材(厚度25μm)與覆蓋膜(Coverlay),實現彎曲半徑≤1mm的柔性連接。輸出Gerber文件、鉆孔文件及BOM表,確保與廠商確認層疊結構、阻焊顏色等細節。

制定設計規格:包括層數、尺寸、材料(如FR-4、高頻材料)、阻抗控制要求、環境適應性(如溫度范圍、濕度)等。例如,高速數字電路可能需要4層以上PCB,并采用低損耗材料以減少信號衰減。2. 原理圖設計元件選型與封裝確認:根據功能需求選擇合適的電子元件,并確認其封裝尺寸、引腳排列是否與PCB設計兼容。例如,BGA封裝元件需考慮焊盤間距和焊接工藝。繪制原理圖:使用EDA工具(如Altium Designer、Eagle、KiCad)繪制電路原理圖,確保元件連接關系正確、標注清晰。設計規則檢查(ERC):通過ERC工具檢查原理圖中的電氣錯誤,如短路、開路、未連接的引腳等。PCB由導電層(銅箔)、絕緣基材(如FR-4)、阻焊層、絲印層等構成。咸寧哪里的PCB設計布局

板材特性:高頻應用選用低損耗材料(如Rogers),普通場景可選FR-4以降低成本。高效PCB設計怎么樣

優化策略:性能、成本與可制造性平衡DFM(可制造性設計)優化焊盤設計:根據元件封裝(如QFN)調整焊盤尺寸(如0.5mm引腳間距的QFN,焊盤長度需比引腳長0.2mm);絲印標注:關鍵元件(如晶振、電感)需標注極性或方向,避免裝配錯誤;測試點設計:在關鍵信號路徑上添加測試點(間距≥100mil),便于生產測試。成本優化方法層數優化:通過優化布局減少層數(如將4層板改為2層板),降低材料成本30%~50%;拼板設計:采用V-Cut或郵票孔拼板,提高SMT貼片效率(如從單板貼片改為4拼板,效率提升300%);替代料分析:通過參數對比(如電容容值、ESR值)選擇性價比更高的元件,降低BOM成本15%~25%。高效PCB設計怎么樣

電源與地網絡設計:采用“星形接地”或“多層平面接地”降低地彈噪聲。電源平面需分割時,通過0Ω電阻或磁珠連接,避免共模干擾。5.設計驗證與輸出DRC/ERC檢查:使用AltiumDesigner、Eagle等工具的規則檢查功能,驗證線寬、間距、孔徑等參數。示例:檢查,避免“孔大于焊盤”錯誤。3D可視化驗證:通過MCAD-ECAD協同工具(如SolidWorksPCB)檢查元件干涉、散熱器裝配空間。輸出文件規范:Gerber文件:包含頂層/底層銅箔、阻焊層、絲印層等(RS-274X格式)。鉆孔文件:Excellon格式,標注孔徑、位置及數量。裝配圖:提供元件坐標、極性標記及貼裝高度(用于S...

- 十堰什么是PCB設計 2025-08-27

- 荊州正規PCB設計包括哪些 2025-08-27

- 咸寧設計PCB設計哪家好 2025-08-27

- 咸寧正規PCB設計哪家好 2025-08-27

- 孝感PCB設計規范 2025-08-25

- 湖北如何PCB設計哪家好 2025-08-25

- 恩施PCB設計多少錢 2025-08-25

- 隨州設計PCB設計批發 2025-08-24

- 荊門了解PCB設計走線 2025-08-24

- 十堰設計PCB設計走線 2025-08-24

- 荊門專業PCB設計批發 2025-08-24

- 孝感哪里的PCB設計規范 2025-08-24

- 襄陽常規PCB設計 2025-08-24

- 高效PCB設計怎么樣 2025-08-24

- 襄陽專業PCB設計銷售電話 2025-08-24

- 恩施如何PCB設計 2025-08-23

- 黃石了解PCB制板功能 08-27

- 荊州正規PCB設計包括哪些 08-27

- 襄陽打造PCB制板哪家好 08-27

- 隨州印制PCB制板布線 08-27

- 黃岡了解PCB制板批發 08-27

- 湖北正規PCB制板包括哪些 08-27

- 咸寧設計PCB設計哪家好 08-27

- 襄陽設計PCB制板銷售 08-27

- PCB制板原理 08-27

- 咸寧正規PCB設計哪家好 08-27